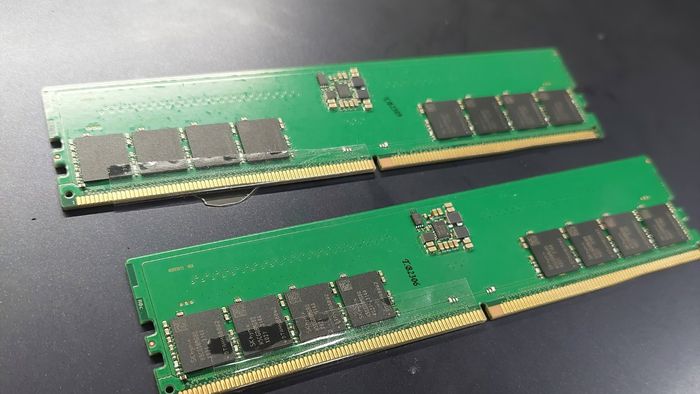

In an era defined by supply chain volatility and the relentless pursuit of cost-efficiency, the semiconductor industry is preparing to take a strategic step back. A consortium of hardware heavyweights—including Intel, ASUS, ASRock, and TeamGroup—has recently introduced HUDIMM, a new memory standard designed to mitigate the ongoing pressures of the RAM market. While the nomenclature suggests evolution, the reality is a deliberate reduction: HUDIMM is essentially the familiar UDIMM architecture with its specifications halved.

The technical compromise lies in the data channels. Where standard DDR5 modules utilize two 32-bit channels to manage data flow, the HUDIMM standard operates on a single 32-bit channel. This architectural thinning allows manufacturers to produce modules with fewer complexities and lower costs, providing a release valve for a market frequently strangled by shortages. It is a pragmatic pivot toward volume, but one that carries a predictable tax on raw throughput.

Initial benchmarks conducted by HKEPC and ASUS illustrate the depth of that performance cost. When testing a 16 GB module at 7,200 MT/s, the transition from the traditional UDIMM to the HUDIMM standard resulted in a significant drop in read performance, nearly halving the effective bandwidth in certain metrics. While latency remains relatively stable, the reduction in available lanes creates a bottleneck that high-performance users will find difficult to ignore. In the current landscape, the industry appears to be betting that for many consumers, a slower module in hand is better than a premium one that remains out of stock.

With reporting from Canaltech.

Source · Canaltech